**PCD4440T**

#### **FEATURES**

- Scrambler or descrambler function

- · Scrambling in frequency domain

- Selectable split frequency (up to 10 selections per second)

- · Telephony-band filtering included

- · No increase in bandwidth

- · No external components required

- Small signal delay

- Insensitive to distortion and group delay of transmission channel

- · Control via serial (I2C) bus

- · Low transfer loss of speech

- · Mute option

- · Transparent mode

- · High signal input impedance

- Low signal output impedance

- · Low power consumption

#### **APPLICATIONS**

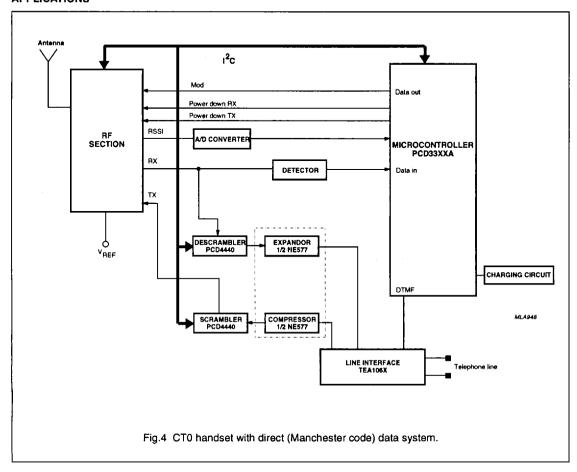

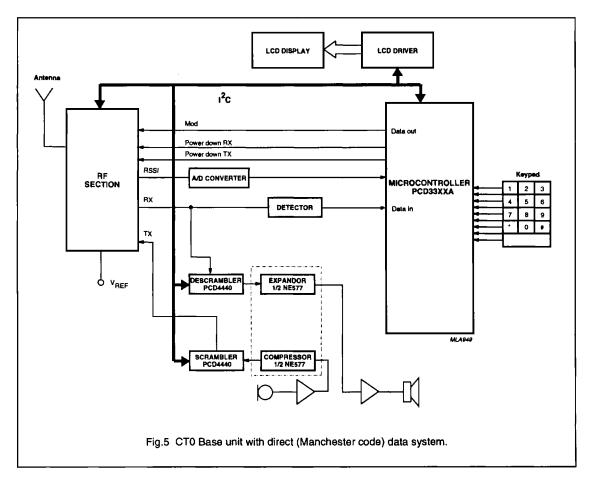

- · Cordless telephones

- · Security telephones

- Portable phones

- PMR

# BUS

### **GENERAL DESCRIPTION**

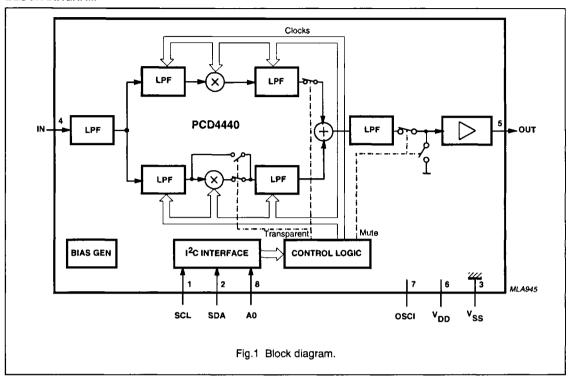

The PCD4440 is a silicon gate CMOS integrated circuit intended to be used in radio, mobile- and line powered telecommunications products utilizing a microcontroller for the control functions. Analog scrambling/descrambling is based on the split frequency method realized in a sophisticated switched-capacitor technology. The PCD4440 is compatible with most microcontrollers and communicates via a two line bidirectional bus (I<sup>2</sup>C).

## **ORDERING INFORMATION**

| EXTENDED TYPE NUMBER | PACKAGE |              |          |         |

|----------------------|---------|--------------|----------|---------|

|                      | PINS    | PIN POSITION | MATERIAL | CODE    |

| PCD4440T             | 8       | mini-pack    | plastic  | SOT176C |

PCD4440T

# **BLOCK DIAGRAM**

PCD4440T

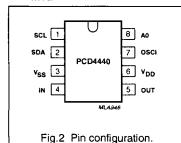

#### **PINNING**

# **FUNCTIONAL DESCRIPTION**

To provide privacy for the end user of a cordless telephone set, the radio-link audio signal must be scrambled. In the microphone and the incoming telephone line audio path a scrambler circuit has to be implemented. Consequently the audio signal to the telephone line and to the earpiece must be descrambled. Both functions can be fulfilled by the PCD4440 by simply inserting it in the audio path.

The PCD4440 accomplishes this task by first filtering the incoming signal, limiting the bandwidth to 3500 Hz. Then the signal is split into a high (>  $f_s$ ) and a low (<  $f_s$ ) frequency band. Both frequency bands are inverted and added again to provide a single output signal.

#### Pin Description

| SYMBOL          | PIN | FUNCTION                             |  |

|-----------------|-----|--------------------------------------|--|

| SCL             | 1   | serial clock line (I <sup>2</sup> C) |  |

| SDA             | 2   | serial data line (I <sup>2</sup> C)  |  |

| V <sub>ss</sub> | 3   | negative Supply                      |  |

| IN              | 4   | signal input                         |  |

| OUT             | 5   | signal output                        |  |

| V <sub>DD</sub> | 6   | positive supply                      |  |

| OSCI            | 7   | oscillator input                     |  |

| A0              | 8   | slave address input (I2C)            |  |

Values for 9 split frequencies f<sub>s</sub> can be controlled by a scramble code table in the microcontroller. Control of these split frequencies is accomplished via the serial two wire I<sup>2</sup>C-bus. In addition to the split frequencies (fs), a transparent mode and mute instruction can be selected.

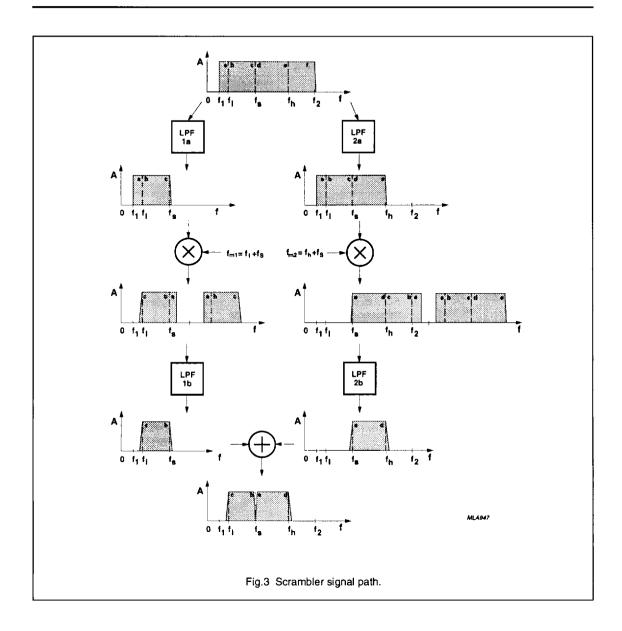

In Fig.3, the signal path for both bands is drawn. The lower band path (on the left side of the diagram) operates on frequencies  $f \le f_s$  (Split Frequency), the upper band path (on the right side) on frequencies  $f \ge f_s$ .

The input signal contains frequencies from  $f_1$  up to  $f_2$ . The output signal is band limited (only in scrambling mode) from  $f_1$  (300 Hz) to  $f_n$  (3500 Hz). In the left path, the

input signal is first limited to  $f_s$ . The following modulator inverts the lower band.  $f_i$  is folded up to  $f_s$ ,  $f_s$  down to  $f_i$ . In general, an input frequency  $f_{in}$  is folded to  $f_{out} = f_s + f_i - f_{in}$ . Finally the folded signal is band limited to  $f_s$  again.

In the right path, the input signal is first limited to  $f_h$ . The following modulator inverts the upper band.  $f_S$  is folded up to  $f_h$ ,  $f_h$  down to  $f_S$ . In general, an input frequency  $f_{in}$  is folded to  $f_{out} = f_S + f_h \cdot f_m$ . Finally, the folded signal is band limited to  $f_h$  again. In the last step, the bands are added and buffered.

In the transparent mode, the input signal is band limited to 3500 Hz. Frequencies form 0 - 300 Hz are not filtered out.

PCD4440T

PCD4440T

## **APPLICATIONS**

PCD4440T

## HANDLING

## **Handling MOS devices**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, it is good practice to take normal precautions appropriate to handling MOS devices.

## **PURCHASE OF PHILIPS I'C COMPONENTS**

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.